STT-RAM for GPU register file

이번에는 강제로 공부하게된 논문 내용을 소개한다.

전형적인 well-organized(?) 된 논문 인거 같아서 적어두려고 한다.

ASP-DAC 에 나온 논문인데, 자세한 정보는 직접 찾아보면 된다.

Main contribution

- MLC STT-RAM 으로 GPU register file을 구성 (기존에는 SRAM)

- MLC 특성상 발생하는 soft-bit 과 hard-bit에 속도 차이를 이용하여, 자주 쓰이는 데이터는 soft-bit에 mapping

- SRAM 보다 느린 write 에서 생기는 패널티를 warp rescheduling으로 최소화

이 정도가 주요 아이디어이다. 차후 설명할 motivation과 해결방법(STT-RAM 사용)이 아주 심플하고, 여기서 생기는 단점을 보완하는 scheme을 넣은 전형적인 흐름의 논문이다.

Motivation

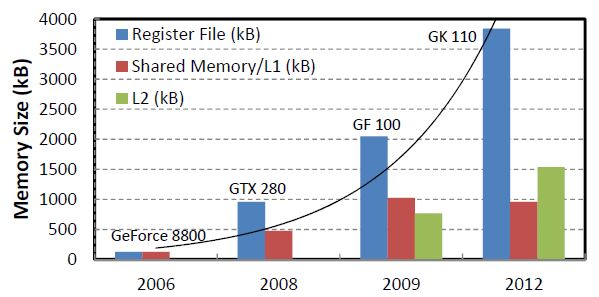

GPU 의 register파일은 매우 크다.

왜냐하면, GPU라는 것이 엄청난 양의 thread를 이용하여 latency를 hiding 하는 구조인데, 이를 위해 재빠른 context switching 이 필요하고, 그 많은 양의 thread들을 유지(?)하기 위해 엄청난 양의 register가 준비되어 있다.

매 아키텍처가 개선될 때마다 register파일이 커지고 있고, SRAM으로 구성되어 area 와 소비 전력이 GPU의 10~20%를 차지한다.

그림 추가!!!!!

그리하여, SRAM보다 구조가 간단하여 면적을 줄일 수 있고, non-volatile 하여 leakage power 가 작은 STT-RAM을 사용하자!

거기에 용량을 더 늘리기 위하여 MLC로 구성하여 쓰자.

SRAM / STT-RAM 비교

STT-RAM은 위에 말한 것과 같은 장점이 있지만 느리다.

자세한 스펙은 표 참조. 특히나 write가 느리다.

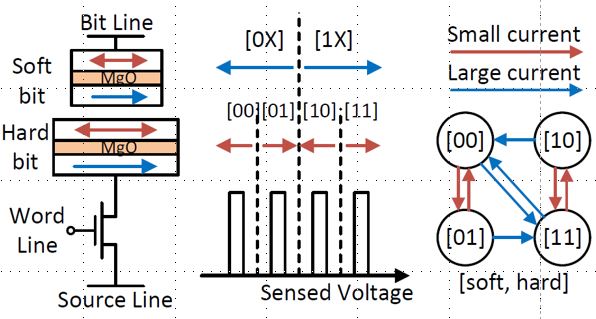

게다가 MLC로 쓰면, soft-bit과 hard-bit의 속도 차이가 있다.

잘하면 soft-bit을 주로 써서 느린 속도를 어느정도는 커버 할수가 있겠다.

Remapping

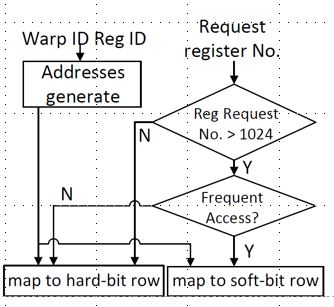

빠른 soft-bit을 잘 활용하기 위하여 remapping 기법을 제안한다. 이것이 활용될 여지가 많은 이유를 간단히 설명하자면, GPGPU application에서 register file은 대부분의 경우에 underutilized 된다(개인적인 직관이다.). 따라서, 반이 soft-bit이고 반이 hard-bit인 MLC의 경우 대부분의 데이터가 soft-bit으로 mapping되어 빠르게 쓸 수 있다.

다시 논문으로 돌아와서, 얘네는 일단 register file이 반보다 적게 쓰면 당연히 무조건 soft-bit만 쓰고, 반보다 많이 쓰는 경우, 즉 hard-bit을 어쩔 수 없이 써야하는 경우에 remapping을 했다.

remapping을 compile time에 많이 쓰이는 register를 profile하여 검사한 후, 그 놈들은 soft-bit으로 몰아주는 식으로 했다.

효과는 엄청났다!

Warp Rescheduling

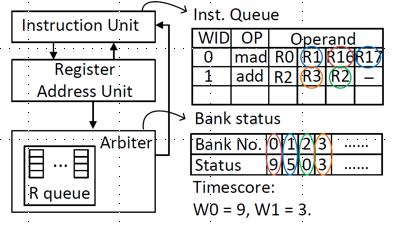

이건 뭐 굳이 설명은 안해도 될 것 같은데, 간단히만 설명하겠다.

write가 느리니, 얼마나 남았는지 counting을 하고 있다가 thread별 critical path(가장 오래기다려야하는 register)기준으로 금방 끝날 놈을 앞으로 땡겨와서 실행하는 것이다.

좀 당연한 것 같은데, 다른 GPU 논문들은 memory, cache 등에 집중한데 반해, register 에서 penalty 가 많이 생기니 register를 기준으로 하겠다는 것이다.

Conclusion

결론적으로 SRAM을 MLC STT-RAM으로 바꿔서 register file을 만들고, 생길수있는 단점을 이러이러하게 보완하니 에너지 효율이 짱짱맨이다.

-이상 이 논문의 주장이었다. 끝.